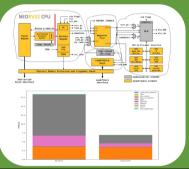

## SparkRV: Open Source Many-Core Digital Neuromorphic Processor

ULP

RISC-V

400000 300000

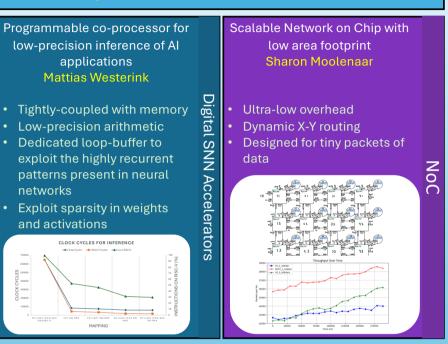

SparkRV (work in progress) is an open-source, manyflexible RISC-V architecture, specifically optimized for low-power, embedded Al applications. Featuring a

design. SparkRV efficiently handles low-power realtime inference and on-device learning tasks by working in event-driven mode. Each independent core integrates a NeoRV RISC-V processor, dedicated data memory, and a specialized accelerator seamlessly interconnected via a scalable network-on-chip (NoC) architecture. Designed to scale effortlessly through chiplet integration, SparkRV facilitates efficient packets, enabling powerful yet energy-efficient neuromorphic computing solutions.

Reducing the power consumption of RISC-V through the instruction loop cache Wiebren Wijnstra

Standard cell-based tiny loop cache

Both dynamic and static

**ULP RISC-V**

NoC

Target technology: Global Foundries FDX 22nm Simulation and verification with Cadence Xcelium (RTL simulation), Genus (area measurement, timing) and Joules (power measurement)

## Please contact us if you want to know more

Inst Mem